——高可靠电路板设计的核心方法论

在电子系统设计中,PCB布线与布局的质量直接影响产品性能、EMC特性和量产良率。本文从工程实践出发,系统解析关键设计要素。

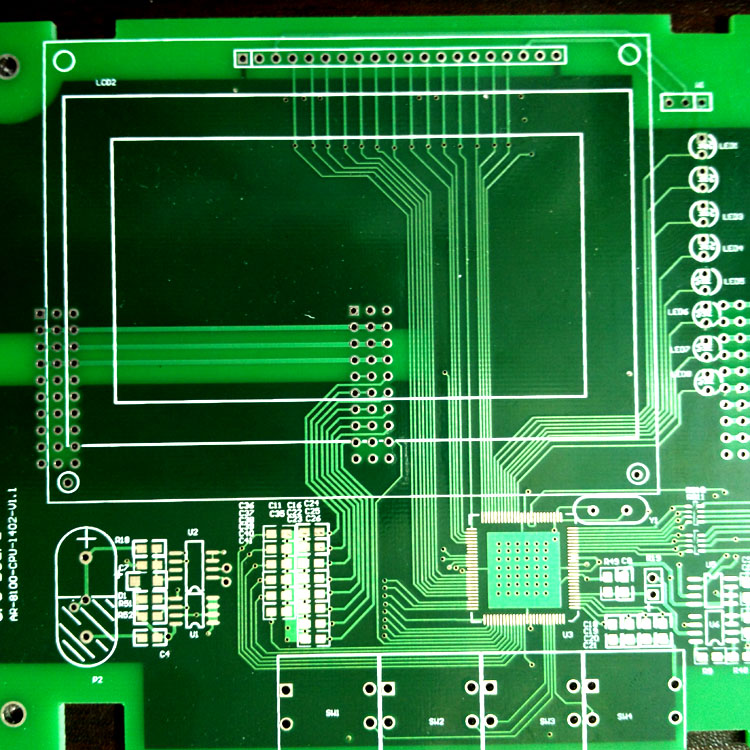

一、布局设计:构建高效信号生态

1. 功能分区策略

三区隔离法则:

电源区(含DC/DC、LDO)

模拟区(传感器/ADC电路)

数字区(处理器/高速逻辑)

典型问题:某工业控制器因电机驱动模块与CAN总线间距不足3mm,导致通信误码率提升20倍

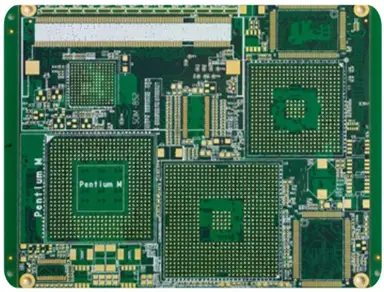

2. 核心器件布局规范

[CPU/FPGA] │ ├─ 去耦电容:0402封装距引脚≤1.5mm ├─ 时钟电路:≥2mm净空区+包地防护 └─ 存储器:DDR3颗粒呈扇形拓扑,长度容差±50mil

散热设计:BGA芯片底部布置9×9过孔阵列(孔径8mil/间距16mil)

3. 电源布局黄金链路

输入滤波 → 开关电源 → 线性稳压 → 负载

关键参数:1oz铜厚承载3A电流需≥80mil线宽

反例:未遵循链式布局的ARM核心板,12V转1.2V压降达0.15V

二、布线关键技术:信号与电源完整性

1. 高速信号控制三要素

| 要素 | 标准值 | 失效后果 |

|---|---|---|

| 差分对长度差 | ≤5mil(0.13mm) | USB3.0丢包率↑30% |

| 阻抗连续性 | 参考层无割裂 | 信号反射↑45% |

| 拐角处理 | 45°或圆弧(≥2倍线宽) | 阻抗突变↑20% |

2. EMC设计三维防护

水平防护:3W原则(并行线距≥3倍线宽)

垂直防护:20H规则(电源层内缩20倍介质厚度)

立体防护:关键信号双面地孔墙(间距λ/20,λ为最高频率波长)

3. 电源完整性(PI)优化

1. 层级化退耦: - 100uF钽电容@电源入口 - 10uF陶瓷电容@子电路 - 0.1uF+0.01uF MLCC@IC引脚 2. 平面分割: - 数字/模拟地单点连接 - 开关电源采用开尔文连接

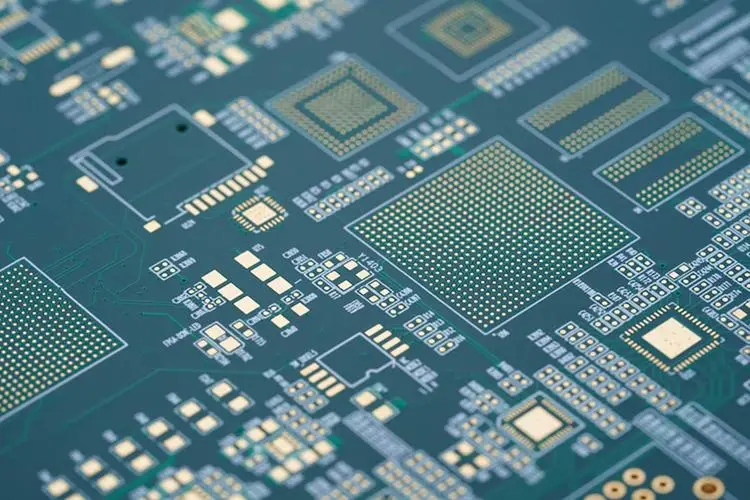

三、可制造性设计(DFM)要点

1. 布线安全规范

| 参数 | 常规板 | 高速板 |

|---|---|---|

| 最小线宽/间距 | 4/4mil | 5/5mil |

| 阻抗公差 | ±15% | ±10% |

| 过孔阻焊桥 | ≥0.1mm | ≥0.15mm |

2. 元件布局禁区

贴片元件间距 ≥ 器件高度的1.5倍

BGA 1mm内禁止放置高器件

波峰焊器件方向统一(平行于传送方向)

3. 散热设计误区

错误做法:MOSFET散热焊盘仅用4个过孔

优化方案:6×6矩阵过孔(孔径:0.3mm/间距:0.8mm)

进阶方案:局部铜嵌块(热阻降低60%)

四、设计验证清单

布局检查

高频/低速电路分区隔离

连接器位置符合装配约束

布线检查

关键网络长度匹配(DDR数据组≤25ps)

电源回路面积最小化

DFM检查

丝印避让焊盘≥0.2mm

测试点覆盖率≥90%

工程实践启示

优秀PCB设计 = 信号完整性 × 电源完整性 × 可制造性

布局阶段解决70%的EMI风险

差分对等长误差每增加1%,信号抖动增加2%

DFM优化投入回报比达1:8(减少改板次数)

掌握核心设计要素,可使电路板良率提升30%以上,EMC测试通过率提高50%。建议使用SI9000进行阻抗预计算,结合板厂工艺能力调整,在方寸之间寻求最优解。

附:常用设计工具

阻抗计算:Polar SI9000

等长布线:Cadence Allegro Constraint Manager

热仿真:Mentor FloTHERM